测试 PCIe(高速外围组件互连)

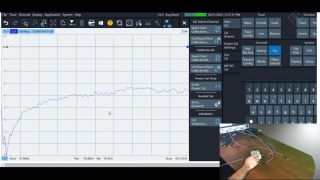

在开发和 PCIe 一致性测试过程中测试 PCIe数据传输和信号属性时,示波器满足很多测试要求。对于物理层,网络分析仪能够执行非常准确的信号完整性测试。利用罗德与施瓦茨专有的自动化网络分析仪测试装置,能够显著缩短信号完整性参数的测试时间,并且更加可靠地测试PCIe 电缆和连接器(具有四个或更多通道,使用 5.0 或 6.0 规范)。

PCIe 是规定服务器或电脑主板互连的事实标准,用于主处理器与集成外设(表面贴装芯片)和插入式外设(扩展卡,例如显卡、内存卡或附加板)之间的互连。对于整个行业中的电脑制造商以及芯片和插件供应商来说,开发过程中的 PCIe 接口验证以及后续的功能验证和生产质量控制是一项重要任务。

PCIe 1.0 于 2003 年首次推出,带宽为 8 GB/s,运行频率为 2.5 GHz,传输速率为 2.5 GT/s,PCI-SIG(特别兴趣小组)每隔几年还会发布新的升级版本,每次都会将性能提高一倍。最新版 PCIe 6.0 标准于 2022 年发布,带宽为 256 GB/s,运行频率为 32 GHz,传输速率为 64 GT/s。数据速率表示为每秒的传输次数,而不是比特率。这是因为标准使用的传输编码将数据位转换为大量的传输字符,以减少传输错误,但这也增加了传输的信息量。PCI 1.0 和 2.0 使用 8b/10b 编码,3.0,使用 128b/130b 编码,大幅降低了传输开销。实现直流平衡和有界差异有助于减少传输错误(从长期来看,“1”和“0”的传输量各占一半)。

虽然 128/130b 将协议开销从 25% 降低到 1.5%,但基于协议的传输纠错也随之减少。PCIe 3.0 增加了接收器均衡,以补偿高频下的通道内频率响应。所使用的复杂算法旨在创建与接收器的通道损耗相匹配的数字滤波器。

PCIe 通过插槽中的 1 个或多个通道进行连接。每个通道包含两对差分信号,一对用于发送数据,一对用于接收数据。因此每个通道都被用作全双工数据流,并传输数据包。PCIe 插槽包含 1 到 32 个通道(通道数量为 2 的幂次方)。通道数标有 x 前缀(例如,x16 代表包含十六个通道的插卡或插槽),其中 x16 是常用的最大尺寸。x1 插槽以每周期 1 位的速度传输数据,x16 插槽以每周期 16 位的速度传输数据。无论是插槽还是版本方面,PCIe 都完全向后兼容,数据速率取决于插槽较小或版本较低的标准。

尽管 PCIe 推出了最新版本,但许多产品仍支持不同的旧版标准。例如,3.0 电脑主板最多,其次是 4.0 主板,5.0 主板最少;要求数据速率超过 16 GT/s 的应用数量非常有限。对于运行多种工业和商业设备的简单处理器,PCIe 1.0 提供的性能远超所需。