验证高速数字设计中 PLL 的加性相位噪声和抖动衰减

提高高速数字设计和无线通信的数据率,需要具有低加性相位噪声和高抖动衰减的串行解串器锁相环 (SerDes PLL) 和时钟合成器。现代设计通常采用由抖动衰减器和频率合成器组成的两级架构。相位噪声分析仪具备一流的相位噪声灵敏度,是执行此类测试的首选仪器。为了激励 PLL,需要具有超低相位噪声的附加信号源。

提高高速数字设计和无线通信的数据率,需要具有低加性相位噪声和高抖动衰减的串行解串器锁相环 (SerDes PLL) 和时钟合成器。现代设计通常采用由抖动衰减器和频率合成器组成的两级架构。相位噪声分析仪具备一流的相位噪声灵敏度,是执行此类测试的首选仪器。为了激励 PLL,需要具有超低相位噪声的附加信号源。

加性相位噪声(残余相位噪声)是指设备在其输入信号的相位噪声中额外添加的相位噪声量。因此,测试装置需要使用拟理想信号源,确保相较于被测设备的加性相位噪声,信号源的相位噪声可以忽略不计,如此被测设备输出端测得的相位噪声将主要为其加性相位噪声。对于现代高速数字应用中的 PLL,此类测量任务愈加困难,并需要具备一流相位噪声性能的信号源。

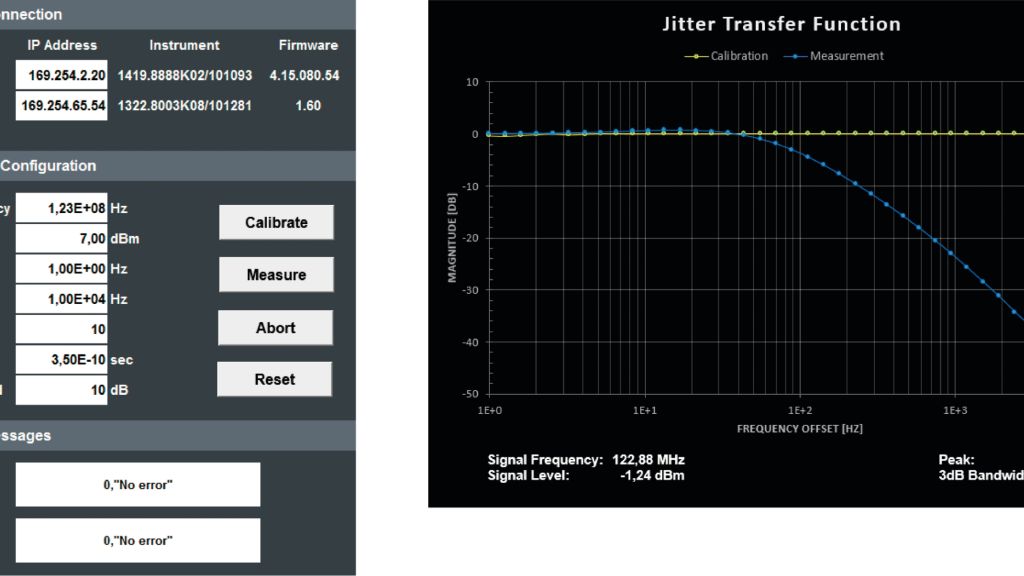

另一个重要参数则为抖动传递函数 (JTF),可显示设备在不同频率偏移条件下的抖动衰减。在被测设备的输入端应用人工离散抖动,并在其输入端和输出端测量此抖动,以计算 PLL 抖动衰减。

R&S®FSWP 相位噪声分析仪和 VCO 测试仪具备业内领先的相位噪声灵敏度,并可使用 R&S®FSWP-B60 互相关和 R&S®FSWP-B61 互相关(低相位噪声)选件进一步提高灵敏度。

此仪器使用 R&S®FSWP-B64 残余相位噪声测量选件,可提供超低相位噪声信号源,便于轻松测量加性相位噪声。

也可使用 R&S®SMA100B 射频和微波信号发生器等外部信号源以激励被测 PLL。R&S®SMA100B 具备卓越的信号纯度和相位噪声性能,并可使用不同的相位噪声性能选件进行扩展。

对于大多数 SerDes PLL 和时钟合成器,与被测设备的加性相位噪声相比,R&S®FSWP-B64 和 R&S®SMA100B 的相位噪声可以忽略不计。R&S®FSWP 测得的相位噪声主要为被测设备的加性相位噪声。

根据 R&S®FSWP-B64 的加性相位噪声测量方法,可以进一步抑制激励信号的相位噪声影响 1)。与其他解决方案不同,此测量方法无需手动确保与外部移相器正交。R&S®FSWP 会自动解决这一问题,在加性相位噪声测量的易用性方面树立了新标准。

R&S®SMA100B 还可用于测量 PLL 的抖动传递函数。通过调相(R&S®SMAB-K720 选件)为信号源添加人工抖动。

R&S®FSWP 测量被测设备输出端的实际抖动,并将其归一化为输入端抖动,从而测定抖动衰减。本应用说明页面提供可供下载的外部工具。此工具支持 R&S®SMA100B(需要 R&S®SMAB-K720 选件)、R&S®FSWP(需要 R&S®FSWP-B60 或 R&S®FSWP-B61 选件)和 R&S®FSPN。它可测量不同频率偏移条件下的抖动衰减,并测定被测设备的抖动传递函数,包括峰值与 3 dB 带宽(参见以下屏幕截图)。

R&S®FSWP 具备所需功能以测试高速数字设计中 PLL 的加性相位噪声。R&S®SMA100B 可用作外部超低相位噪声信号源,并可测量 PLL 的抖动传递函数 (JTF)。

自动测量抖动传递特性