数字设计测试

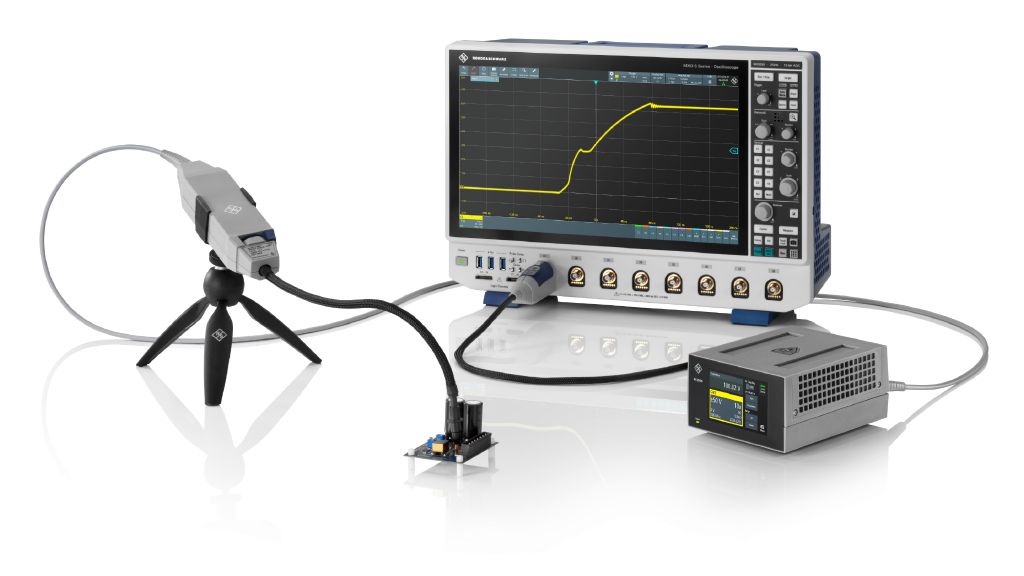

用于设计验证和调试的数字设计测试解决方案

技术在快速更新迭代,高速数字标准同样需要不断发展,才能紧跟潮流,保持强大的行业洞察力。电子工程师需要设计和开发集成电路板架构,以便满足这些严格的要求。每一代电子设备都会给数字设计的性能带来新的挑战。如果您希望确保数字系统设计符合日益严格的标准,能够应对不断出现的挑战,需要在从设计到完整一致性测试的所有产品开发阶段测试设计。数字设计测试解决方案必须涵盖包括互连产品在内的多种设计系统,并提供各种测试工具以执行抖动测试等不同的测量任务。

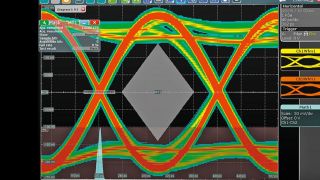

信号完整性和 电源完整性在数字设计中至关重要。数据速率提高、电源电压减小、集成密度增加,要求降低信号和时钟的抖动与噪声阈值。这也会给传输通道造成更大的损害(例如引起频率相关损耗、反射和串扰),并且会加剧电压暂降和地弹对电源路径的影响。此外,电源电压减小会持续削弱电源路径的抗干扰性,使信号和时钟出现抖动和幅度噪声。