触发 DDR3 存储器的读写周期

分析 DDR 接口的信号完整性性能时,分离读写周期是一项严峻挑战。这需要全面的触发功能,尤其是在实时重建眼图时。

分析 DDR 接口的信号完整性性能时,分离读写周期是一项严峻挑战。这需要全面的触发功能,尤其是在实时重建眼图时。

DDR 接口的信号质量是确保存储系统可靠工作的关键。数据眼图分析是评估信号完整性的常见方法。DDR 架构采用半双工操作,读周期和写周期以不同的时间间隔出现在相同的信号迹线上。为区分读写周期以进行眼图分析,工程师需要了解数据 (DQ) 和选通信号 (DQS) 的相位对齐情况。使用专用触发功能来分离读写周期是一项严峻挑战,但可以实时评估长时间的数据眼图。

读写周期

R&S®RTP 高性能示波器具备高级触发功能。独特的数字触发系统采用 A-B 序列,可设置两个连续触发条件,并具有精确的时间延迟和低至 1 ps 的分辨率。触发条件可与其他通道的逻辑限定组合使用。此外,用户可以使用 R&S®RTP-K19 区域触发选件直观定义符合触发条件的区域,简化设置。

读写周期

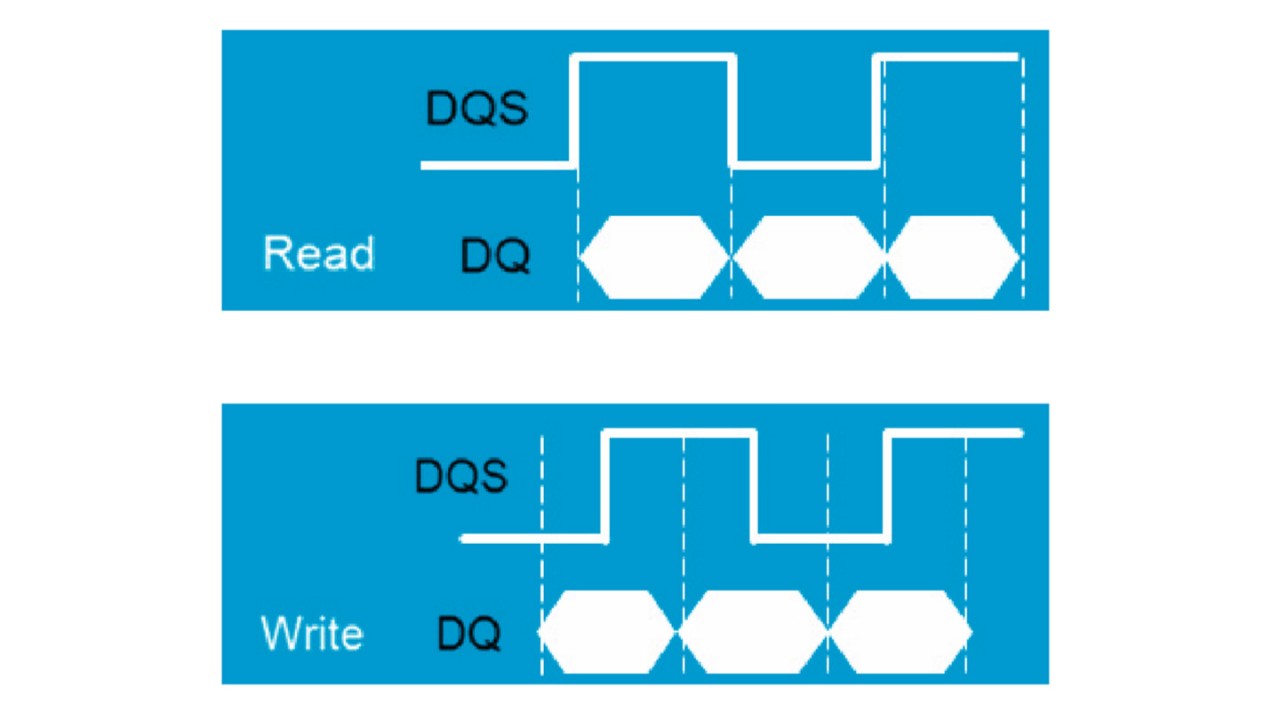

DDR 存储器接口的读写周期并未相位对齐。该架构需要存储控制器提供差分选通信号 (DQS),以便在高速或低速稳定运行时锁存数据 (DQ)。在读周期内,DRAM 发送出同相 DQS 和 DQ 至存储控制器,但在写周期内则存在 0.5 单位间隔 (UI) 偏移。

设置 A-B 触发延迟

利用写周期内的相位关系,A 触发事件可以定义为 DQ 信号的边沿触发。延迟和重置机制会限制该触发事件,以便检查 DQS 信号的 B 边沿触发事件。检查 B 事件的延迟不得超过 ½ UI。

A 事件还可定义为窗口触发,以便从三态序列返回后检测第一个 DQ 位(窗口宽度 > 1 UI)。

触发 DQS 前置码

对于 DDR3,写周期内 DQS 前置码位为正,读周期内则为负。与数据位宽相比,DRAM 控制器的前置码位宽通常稍有不同。可据此区分触发。只需定义超过 1 UI 的脉冲宽度触发,或将范围规定为 1 UI 至 1.5 UI。由于前置码实施机制不同,因此建议先查看设备的前置码时序特性。

触发 DQS 前置码

对于 DDR3,写周期内 DQS 前置码位为正,读周期内则为负。与数据位宽相比,DRAM 控制器的前置码位宽通常稍有不同。可据此区分触发。只需定义超过 1 UI 的脉冲宽度触发,或将范围规定为 1 UI 至 1.5 UI。由于前置码实施机制不同,因此建议先查看设备的前置码时序特性。

区域触发

R&S®RTP 具备可选区域触发功能,可根据独特的波形形状确定有效的读写周期。可以直接在屏幕上自定义区域,以辨别信号是否应该通过区域。当波形特性不在触发定义范围内时,此功能尤其有用。

在写周期内,DQS 与 DQ 异相。可以定义区域以确保 DQ 信号与 DQS 不超出相同边沿。

通常通过 DRAM 测量 DDR 存储器的信号完整性。这意味着写信号的电压幅度低于读信号。因此,区域可以根据信号强度(电压电平)筛除读周期。

评估 DDR 存储器接口的信号完整性时,必须可靠地分离读写周期。R&S®RTP 高性能示波器具备数字触发功能,可确保精确的序列触发机制。此功能可与区域触发功能结合使用,为 DDR 存储器接口测量提供多种灵活的触发功能。